Citao sam vec o ovom kolu. Ono sto sam do sada utvrdio je da kristal na 5.76MHz radi, kao i onaj u oscilatoru od 14.7MHz (izmereno frekvencmetrom).

Medjutim, nemam odgovarajucu sondu za vise frekvencije, pa ne mogu tacno proveriti sta izlazi na tacki TP2.

Ako sam dobro razumeo, tu bi trebalo biti oko 14.7*9 = oko 132MHz?

+5V, +8V i -6V naponski nivoi su u redu.

D/A iz CPU-a salje odgovarajuce naponske nivoe ofset oscilatoru (TP6).

Tacka TP1 bi po pravilu trebala biti na 3-4V, medjutim, voltmetar tu ne pokazuje nista, cak i promenom kapaciteta CV1.

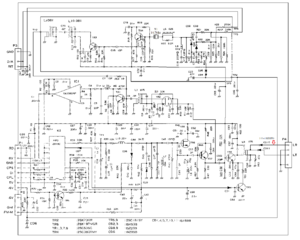

Ono kako sam razumeo ovo kolo (uPD2819C) je sledece:

- referentni signal je 5.76MHz

- signal za komparaciju stize na pin 14 (iz TA7060AP)

- ako postoji neka razlika, menja se izlazni napon na pinu 8, sto dalje utice na varikap diodu CD8, a ujedno i ukljucuje oscilatorni deo TR6,7 i 8.

- preko C12 i TR2 se signal vraca nazad, na "proveru"

Ispravite me ako gresim.

Inace - preporuka za sondu za frekvencmetar do 500MHz, 50oma/5V max?

YU2MP

PLL sema - princip rada

PLL sema - princip rada